# nterfacing the DP8420A/21A/22A to the 68000/008/010

# Interfacing the DP8420A/21A/22A to the 68000/008/010

National Semiconductor Application Note 538 Joe Tate and Rusty Meier May 1989

### INTRODUCTION

This application explains note interfacing DP8420A/21A/22A DRAM controller to the 68000. Three different designs are shown and explained. It is assumed that the reader is familiar with the 68000 access cycles and the DP8420A/21A/22A modes of operation. This application note also applies to the 68010.

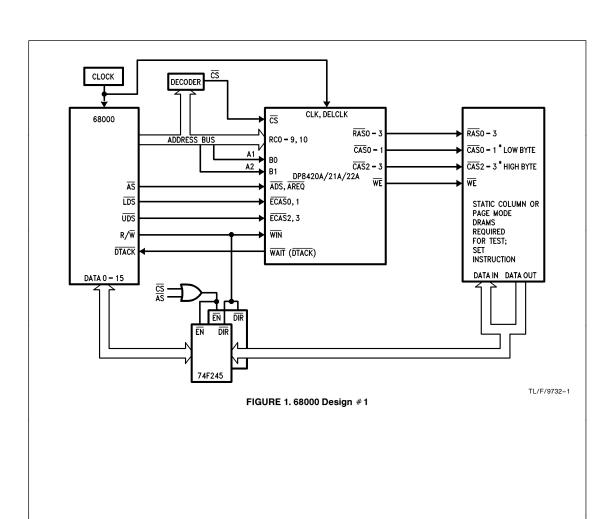

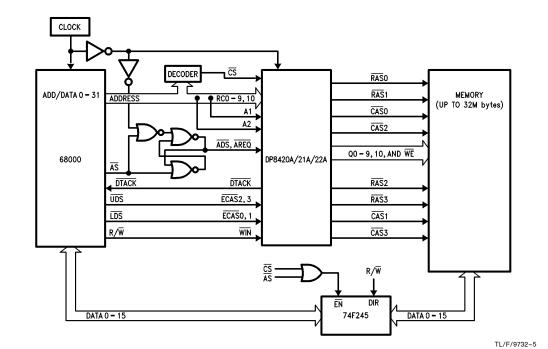

### **DESIGN #1 DESCRIPTION**

Design #1 is a simple circuit to interface the 68000 to the DP8420A/21A/22A and up to 32 Mbytes of DRAM. The DP8420A/21A/22A is operated in Mode 1. An access cycle begins when the 68000 places a valid address on the address bus and asserts the address strobe (AS). Chip select (CS) is generated by a 74AS138 decoder. If a refresh or Port B access (DP8422A only) is not in progress, the DP8420A/21A/22A will assert the proper RAS depending on the bank select inputs (B0, B1). After guaranteeing the programmed value of row address hold time the DP8420A/21A/22A will switch the DRAM address (Q0-8, 9, 10) to the column address and assert CAS. By this time, the 74AS245's have been enabled and the DRAMs place their data on the data bus. The DP8420A/21A/22A also asserts DTACK which is used to generate DTACK to the 68000 to complete the access.

If a refresh or Port B access had been in progress, the DP8420A/21A/22A would have delayed the 68000's access by inserting wait states into the access cycle until the refresh or Port B access was complete and the programmed amount of precharge time was met. This circuit can run up to 10 MHz with 0 wait states, with two or more banks. For 10 MHz, zero wait states with one bank, see

Timing parameters are referenced to the numbers shown in the DP8420A/21A/22A data sheet timing parameters. Numbered times starting with a "\$" refer to the DP8420A/21A/22A timing parameters. Numbered times starting with "#" refer to the 68000 data sheet. Equations have been given to allow the user to calculate timing based on his frequency and application. The clock is at 10 MHz, a multiple of 2 MHz, allowing it to be tied directly to DELCLK. If DELCLK is not a multiple of 2 MHz, ADS to CAS must be recalculated.

### **DESIGN #1 TIMING AT 10 MHz AND 8 MHz**

Clock Period = Tcp10 = 100 ns @ 10 MHz = Tcp8 = 125 ns @ 8 ns

\$400b: ADS Asserted Setup to CLK High

= Clock Period - CLK High to AS Asserted

= Tcp10 - #9

= 100 ns - 55 ns

= 45 ns @ 10 MHz

= Tcp8 - #9

= 125 ns - 60 ns

= 65 ns @ 8 MHz

CS Setup to ADS Asserted \$401

68000 Address to AS Max

74AS138 Decoder

#11 - Tphl Max

= 20 ns - 9 ns

= 11 ns @ 10 MHz

#11 - Tphl

= 30 ns - 9 ns

= 21 ns @ 8 MHz

\$407 & \$404: Address Valid Setup to ADS Asserted

= 68000 Address to AS Max

= #11 Max

= 20 ns @ 10 MHz

= #11 Max

= 30 ns @ 8 MHz

ADS Negated Held from CLK High \$405:

68000 CLK High to AS Asserted Min

= #10 Min

= 0 ns @ 10 MHz

= #10 Min

= 0 ns @ 8 MHz

#47: DTACK Setup Time

> = 1/2 Clock Period Clock to DTACK Asserted

$= \frac{1}{2} \text{Tcp10} - \$18$

= 50 ns - 28 ns

= 22 ns @ 10 MHz \*\*Using 8420-25

$= \frac{1}{2} \text{Tcp8} - \$18$

= 62.5 ns - 33 ns

= 29.5 ns @ 8 MHz \*\*Using 8420-25

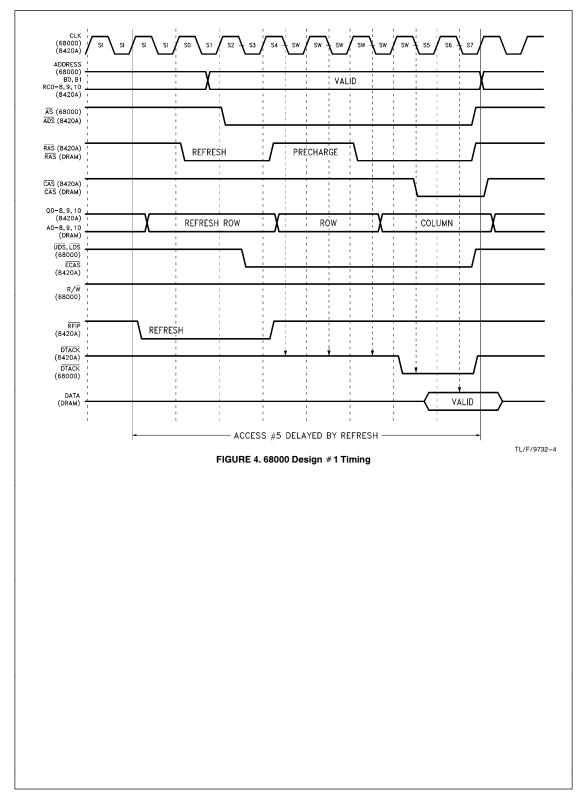

### **RAS LOW DURING REFRESH**

tRAS = Programmed Clock

- [CLK High to Refresh RAS Asserted)

(CLK High to Refresh RAS Negated)]

= Tcp10 + Tcp10 - \$55

= 100 ns + 100 ns - 6 ns

= 194 ns @ 10 MHz

= Tcp8 + Tcp8 - \$55

= 125 ns + 125 ns - 6 ns

= 244 ns @ 8 MHz

### **RAS PRECHARGE PARAMETERS\*\***

tRP = (Programmed Clocks - 1) [(AREQ to RAS Negated) (CLK to RAS Asserted)] = Tcp10 - \$50

= 100 ns - 16 ns

= 84 ns @ 10 MHz

= Tcp8 - \$50= 125 ns - 16 ns

= 109 ns @ 8 MHz

\*\*To gain more precharge program 3t or use design #2.

### **trac and tcac for drams**

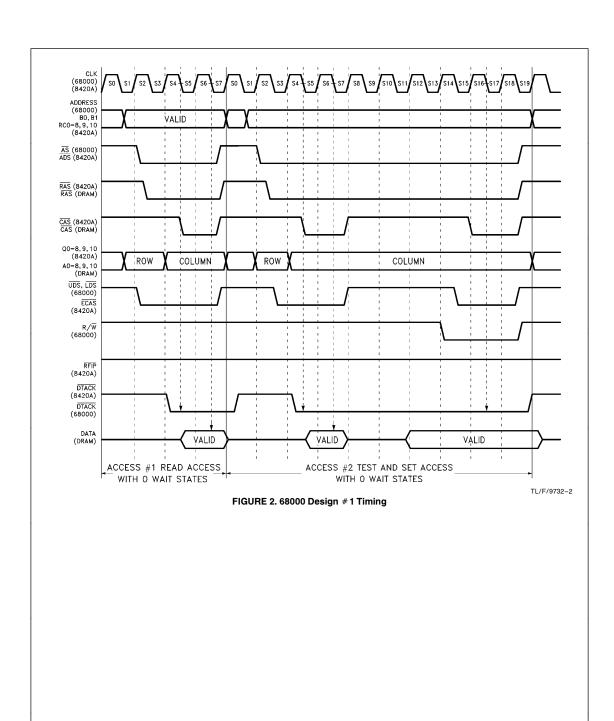

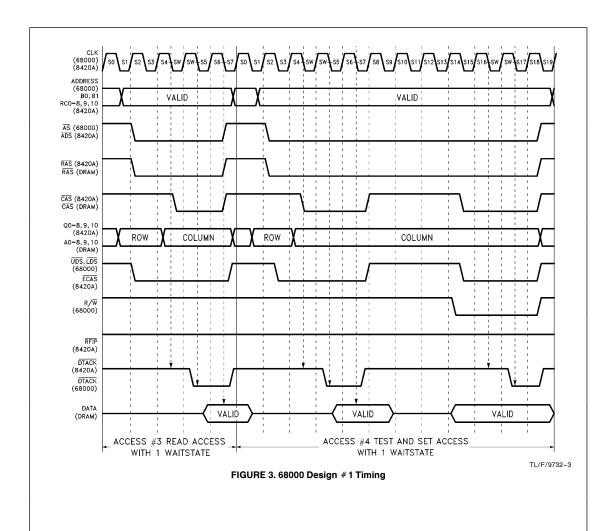

Timing is supplied for the system shown in Figure 1. (see Figures 2, 3 and 4). Since systems and DRAM times vary, the user is encouraged to change the following equations to match his system requirements. Timing has been supplied for systems with 0 or 1 wait state. If DELCLK is not a multiple of 2 MHz, the timing for tRAH and tASC will increase or decrease according to the equations given in the data sheet. The  $\overline{ADS}$  to  $\overline{RAS}$  and  $\overline{ADS}$  to  $\overline{CAS}$  will also have to be changed depending on the capacitance of the DRAM array.

### 0 Wait States

= s2 + s3 + s4 + s5 + s6 - CLK to  $\overline{AS}$ tRAC Asserted Max -  $\overline{\text{ADS}}$  Asserted to  $\overline{\text{RAS}}$ Asserted - 74AS245 Delay Max 68000 Data Setup Min = 2½ Tcp10 - #9 - \$402 − Tphl Max − #27 = 250 ns - 55 ns - 35 ns - 7 ns- 10 ns Using 8420-20 = 143 ns @ 10 MHz w/Heavy Load  $= 2\frac{1}{2} \text{Tcp8} - #9 - $402$ \_ Tphi Max - #27 = 312.5 ns - 60 ns - 35 ns

− 7 ns − 15 ns

= 195 ns @ 8 MHz

Using 8420-20

w/Heavy Load

### 1 Wait State

tRAC

= s2 + s3 + s4 + sw + sw + s5 + s6- CLK to  $\overline{\mathsf{AS}}$  Asserted Max -  $\overline{\mathsf{ADS}}$ Asserted to  $\overline{RAS}$  Asserted - 74AS245 Delay Max - 68000 Data Setup Min  $= 3\frac{1}{2} \text{Tcp10} - #9 - $402 - \text{Tphl}$ Max - #27 = 350 ns - 55 ns - 35 ns - 7 ns- 10 ns Using 8420-20 = 243 ns @ 10 MHz w/Heavy Load  $= 3\frac{1}{2} \text{ Tcp8} - #9 - $402$  Tphl Max - #27 = 437.5 ns - 60 ns - 35 ns - 7 ns- 15 ns Using 8420-20 = 320 ns @ 8 MHz w/Heavy Load

### 0 Wait States

tCAC

$= \text{s2} + \text{s3} + \text{s4} + \underline{\text{s5}} + \text{s6} - \text{CLK to } \overline{\text{AS}} \\ \text{Asserted Max} - \overline{\text{ADS}} \text{ Asserted to } \overline{\text{CAS}}$ Asserted - 74AS245 Delay Max - 68000 Data Setup Min

$= 2\frac{1}{2} \text{Tcp10} - #9 - $403a$ \_ Tphl Max - #27

= 250 ns - 55 ns - 94 ns - 7 ns

- 10 ns

Using 8420-20 = 84 ns @ 10 MHz w/Heavy Load

$= 2\frac{1}{2} \text{ Tcp8} - #9 - $403a$

- Tphl Max - #27

= 312.5 ns - 60 ns - 94 ns - 7 ns

15 ns

= 136 ns @ 8 MHz

Using 8420-20 w/Heavy Load

# 1 Wait State

tCAC

= s2 + s3 + s4 + sw + sw + s6 - CLKto  $\overline{\text{AS}}$  Asserted Max -  $\overline{\text{ADS}}$  Asserted to CAS Asserted - 74AS245 Delay Max - 68000 Data Setup Min

$= 3\frac{1}{2} \text{Tcp10} - #9 - $403a$ - Tphl Max - #27

= 350 ns - 55 ns - 94 ns

− 7 ns − 10 ns

Using 8420-20 = 184 ns @ 10 MHz w/Heavy Load

$= 3\frac{1}{2} \text{Tcp8} - #9 - $403a$

– Tphl Max – #27

= 437.5 ns - 60 ns - 94 ns

- 7 ns - 15 ns

= 261 ns @ 8 MHz

Using 8420-20 w/Heavy Load

|                  | Design #1 Programming Bits                                  |                            |  |  |  |

|------------------|-------------------------------------------------------------|----------------------------|--|--|--|

| Bits Description |                                                             | Value                      |  |  |  |

| R0, R1           | RAS Low Time During REFRESH = 2T RAS Precharge Time = 2T    | R0 = 0<br>R1 = 1           |  |  |  |

| R2, R3           | DTACK Generation Modes<br>for Non-Burst Accesses            | R2 = s<br>R3 = s           |  |  |  |

| R4, R5           | DTACK Generation Modes<br>for Burst Accesses                | R4 = s<br>R5 = s           |  |  |  |

| R6               | Add Wait States with WAITIN                                 | R6 = s                     |  |  |  |

| R7               | DTACK Mode Select                                           | R7 = 1                     |  |  |  |

| R8               | Non Interleaved Mode                                        | R8 = 1                     |  |  |  |

| R9               | Staggered or All RAS REFRESH                                | R9 = u                     |  |  |  |

| C0, C1, C2       | Divisor for DELCLK                                          | C0 = s<br>C1 = s<br>C2 = s |  |  |  |

| C3               | +30 REFRESH                                                 | C3 = 0                     |  |  |  |

| C4, C5, C6       | RAS, CAS Configuration Mode *Choose All CAS Mode            | C4 = u<br>C5 = u<br>C6 = u |  |  |  |

| C7               | Select 0 ns Column Address Setup                            | C7 = 1                     |  |  |  |

| C8               | Select 15 ns Row Address Setup                              | C8 = 1                     |  |  |  |

| C9               | CAS is Delayed to the Next Rising<br>CLK Edge During Writes | C9 = 1                     |  |  |  |

| В0               | The Row/Column Bank Latches<br>Are Fall Through Mode        | B0 = 1                     |  |  |  |

| B1               | Access Mode 1                                               | B1 = 1                     |  |  |  |

| ECAS0            | CAS Not Extended Beyond RAS                                 | ECASO = 0                  |  |  |  |

| u = user defined |        | s = system dependent |                                                        |

|------------------|--------|----------------------|--------------------------------------------------------|

| R2 = 1           | R3 = 0 |                      | for 0 WAIT STATES                                      |

| R2 = 1           | R3 = 0 | R6 = 0               | for 1 WAIT STATE                                       |

| C0 = 1           | C1 = 0 | C2 = 1               | for 10 MHz                                             |

| C0 = 0           | C1 = 0 | C2 = 1               | for 8 MHz                                              |

| R4 = 0           | R5 = 0 |                      | for 0 WAIT STATES during write portion of test and set |

| R4 = 1           | R5 = 1 |                      | for 1 WAIT STATE during write portion of test and set  |

### **DESIGN #2 DESCRIPTION**

Design #2 differs from Design #1 in that the 68000 can be run up to 12.5 MHz. This design can also run with no wait states at 10 MHz if only one bank of DRAM is being used. A latch must be used with the 68000 address strobe to guarantee the address setup to ADS asserted requirement of the DP8420A/21A/22A. Again, the DP8420A/21A/22A is operated in Mode 1.

An access cycle begins when the 68000 places a valid address on the address bus at the beginning of processor state s1. At processor state s2, the 68000 asserts the address strobe, AS. This signal is qualified with CLK low to set a latch. The output of this latch produces the signal ADS to the DP8420A/21A/22A. When the signal  $\overline{\text{ADS}}$  is asserted on the DP8420A/21A/22A, the chip will assert RAS. After guaranteeing the row address hold time, the 8420A/21A/22A will place the column address to the DRAM address bus. After guaranteeing the column address setup time, the DP8420A/21A/22A will assert CAS. After time tCAC has passed, the DRAM will place its data on the data bus. The 8420A/21A/22A will assert the DTACK output allowing the bus cycle to end.

If a refresh of a Port B access had been in progress, the access would have been delayed by inserting wait states in the Port A access cycle.

### DESIGN #2 TIMING AT 12.5 MHz

Clock Period = Tcp12 80 ns @ 12.5 MHz

\$400b:

ADS Asserted Setup to CLK High

- = Clock Period + 1/2 Clock Period + 74AS04 Delay Min + 74AS04 Delay Min - Clock to AS Asserted Max - 74AS04 Delay Min - 74AS02

- Delay Max 74AS02 Delay Max = Tcp12 + 1/2 Tcp12 + Tphl Min

- + Tphl Min #9 Tphl Min

- Tphl Max

Tphl Max

- = 80 ns + 40 ns + 1 ns + 1 ns 55 ns- 1 ns - 4.5 ns - 4.5 ns

# = 57 ns @ 12.5 MHz

\$401

CS Setup to ADS Asserted

- = Clock Period + 74AS04 Delay Min + 74AS04 Delay Min + 74AS02 Delay Min + 74AS02 Delay Min - 74AS04 Delay Min - Clock to ADR Max - 74AS138 Delay Max

- = Tcp12 + Tphl Min + Tphl Min + Tphl Min + Tphl Min - Tphl Min

- #6 Tphl Max

- = 80 ns + 1 ns + 1 ns + 1 ns + 1 ns- 1 ns - 55 ns - 9 ns

= 19 ns @ 12.5 MHz

\$407 & \$404: Address Valid to ADS Asserted

- = Clock Period + 74AS04 Delay Min + 74AS04 Delay Min + 74AS02 Delay Min + 74AS02 Delay Min - Clock to ADR Max - 74AS04 Min

- = Tcp12 + Tphl + Tphl + Tphl + Tphl #6 - Tphl

- = 80 ns + 1 ns + 1 ns + 1 ns + 1 ns- 55 ns - 1 ns

### = 28 ns @ 12.5 MHz

\$405:

ADS Negated Held from CLK High

- = Min 74AS04 + Min 74AS02 + Min 74AS02 + Min 74AS04

- Min 74AS04

- = TphI + TphI + TphI + TphI TphI

- = 1 ns + 1 ns + 1 ns + 1 ns 1 ns

### = 3 ns @ 12.5 MHz

# 47: DTACK Setup Time

- = 1 Clock Period CLOCK skew (74AS04)

- Max Clock to DTACK

- = Tcp12 Tphl Max \$18

- = 80 ns 5 ns 28 ns

- = 47 ns @ 12.5 MHz

### **RAS** LOW DURING REFRESH

tRAS

- = Programmed Clock

- (CLK High to Refresh RAS Asserted)

- (CLK High to Refresh RAS Negated)]

- = Tcp12 + Tcp12 \$55

- = 80 ns + 80 ns 6 ns

- = 154 ns @ 12.5 MHz

### **RAS PRECHARGE PARAMETERS**

- = Programmed Clocks Clock to  $\overline{\mathsf{AS}}$ Negated – [(AREQ to RAS Negated)

- (CLK to RAS Asserted)]

- = Tcp12 + Tcp12 \$50

- = 80 ns + 80 ns 16 ns

- = 144 ns @ 12.5 MHz

\$29b:

AREQ Negated Setup to CLK

- = Clock Period + Min CLOCK Skew 74AS04 - Max 74AS02

- Max 74AS02

- = Tcp12 + Tphl + Tphl Tphl

- = 80 ns + 1 ns 4.5 ns 4.5 ns

= 72 ns @ 12.5 MHz

### **tRAC AND tCAC FOR DRAMs**

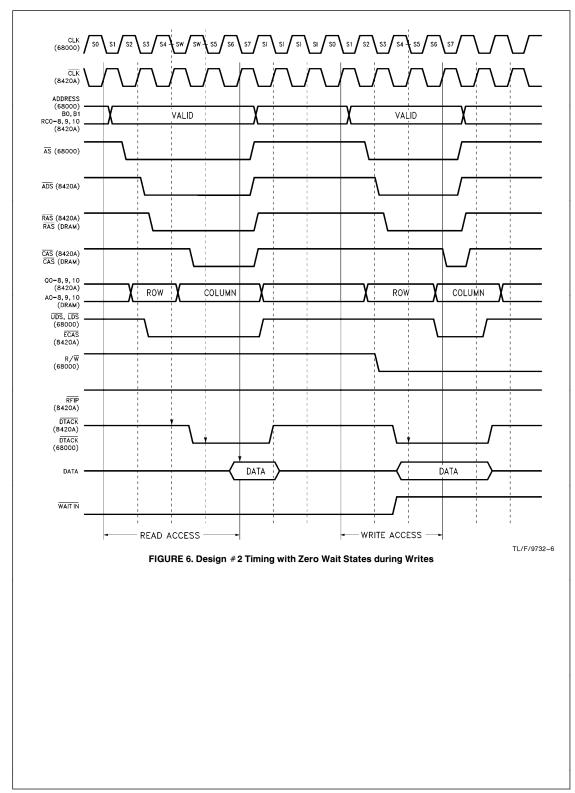

Timing is supplied for the system shown in Figure 5. (See Figures 6 ). Since systems and DRAM times vary, the user is encouraged to change the following equations to match his system. Timing has been supplied for systems with 0 wait states and 1 bank of DRAM and 1 wait state and 4 banks of DRAM. If DELCLK is not a multiple of 2 MHz, the times of tRAH and tASC will increase or decrease according to the equations given in the data sheet. The  $\overline{\text{ADS}}$  to  $\overline{\text{RAS}}$  and  $\overline{\text{ADS}}$  to  $\overline{\text{CAS}}$  will also have to be changed depending on the capacitance of the DRAM array.

### tRAC

### tCAC

0 wait states \* does not use transceivers \*

tCAC =

$$s2 + s3 + s4 + s5 + s6 - 74AS02$$

$Max - 74AS02 Max - Clock to \overline{AS}$

$Max - \overline{ADS}$  Asserted to  $\overline{CAS}$

$- Data Setup$

=  $21/2 Tcp12 - Tphl - Tphl - \#9$

$- \$403a - \#27$

=  $200 ns - 4.5 ns - 4.5 ns - 55 ns$

$- 75 ns - 10 ns$

=  $51 ns @ 12.5 MHz$  \*Using 8420-25  $w$ /Light Load

1 wait state \* uses transceivers \*

tCAC = s2 + s3 + s4 + sw + sw + s5 + s6

- 74AS02 Max Delay - 74AS02 Max

Delay - Clock to

$$\overline{AS}$$

Max -  $\overline{ADS}$

Asserted to  $\overline{CAS}$  - 74AS245 Data Setup

= 3½ Tcp12 - Tphl - Tphl - #9

- \$403a - Tphl - #27

= 280 ns - 4.5 ns - 4.5 ns - 55 ns

- 75 ns - 7 ns - 10 ns

= 124 ns @ 12.5 MHz

### DESIGN #2,0 WAIT STATES DURING WRITE ACCESS

Design #2 can be modified to allow 0 wait states during writes. To accomplish this, the chip must be programmed with the same value except that bits R2, R3 and R6 are changed to:

```

R2 = 0 DTACK of 0T from RAS

R3 = 0

R6 = 0 Hold off DTACK 1 extra clock period

```

The hardware must be modifed. The signal R/W from the 68000 is inverted and tied to the 8420 signal WAITIN. This ensures that a wait state will only be asserted during read accesses (see *Figure 6*).

0 waits during write access timing

### **RAS** Low Time

## **CAS** Low Time

```

tCP  = s2 + s3 + s4 + s5 + s6 - Max CLK

to \overline{AS} - 74AS02 - 74AS02 - Max

\overline{AS} to \overline{CAS} + Min CLK to \overline{DS} + Min ECAS to CAS  = 21/2 \text{ Tcp12} - \#9 - \text{TphI} - \text{TphI}

- \$403a + \#12 + \$14

= 200 \text{ ns} - 55 \text{ ns} - 4.5 \text{ ns} - 4.5 \text{ ns}

- 82 \text{ ns} + 0 \text{ ns} + 0 \text{ ns}

= 54 \text{ ns} @ 12.5 \text{ MHz}

```

|                  | Design #2 Programming Bits                                  |                               |  |  |  |

|------------------|-------------------------------------------------------------|-------------------------------|--|--|--|

| Bits Description |                                                             | Value                         |  |  |  |

| R0, R1           | RAS Low Time = 2T RAS Precharge Time = 2T                   | R0 = 0<br>R1 = 1              |  |  |  |

| R2, R3           | DTACK Generation Modes<br>for Non-Burst Accesses            | R2 = 0<br>R3 = 1              |  |  |  |

| R4, R5           | DTACK Generation Modes<br>for Burst Accesses                | R4 = 0<br>R5 = 1              |  |  |  |

| R6               | Add Wait States with WAITIN                                 | R6 = 0                        |  |  |  |

| R7               | DTACK Mode Select                                           | R7 = 1                        |  |  |  |

| R8               | Non Interleaved Mode                                        | R8 = 1                        |  |  |  |

| R9               | Staggered or All RAS REFRESH                                | R9 = u                        |  |  |  |

| C0, C1, C2       | Divisor for DELCLK                                          | C0 = u<br>C1 = u<br>C2 = u    |  |  |  |

| C3               | +30 REFRESH                                                 | C3 = 0                        |  |  |  |

| C4, C5, C6       | RAS, CAS Configuration Mode *Choose All CAS Mode            | C4 = u<br>C5 = u<br>C6 = u    |  |  |  |

| C7               | Select 15 ns Column Address Setup                           | C7 = 1                        |  |  |  |

| C8               | Select 15 ns Row Address Setup                              | C8 = 1                        |  |  |  |

| C9               | CAS is Delayed to the Next Rising<br>CLK Edge During Writes | C9 = 1                        |  |  |  |

| В0               | The Row/Column Bank Latches<br>Are Fall Through Mode        | B0 = 1                        |  |  |  |

| B1               | Access Mode 1                                               | B1 = 1                        |  |  |  |

| ECAS0            | CAS Not Extended Beyond RAS                                 | $\overline{\text{ECASO}} = 0$ |  |  |  |

# $u = user \ defined$

<sup>\*</sup>see previous page for 0 WAIT STATES during writes

FIGURE 5. 68000 Design #2 up to 12.5 MHz

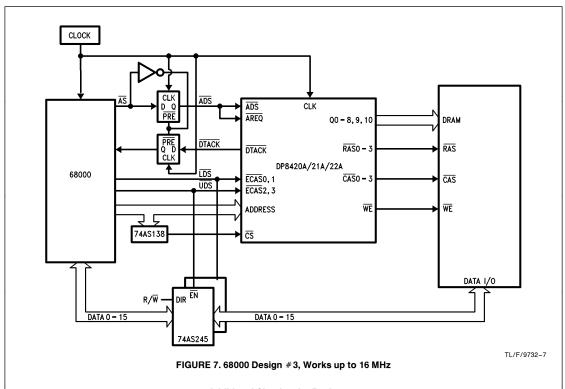

### **DESIGN #3 DESCRIPTION**

Design #3 is a simple circuit to interface the 68000 running @ 16 MHz to the DP8420A/21A/22A and up to 32 Mbytes of DRAM. The DP8420A/21A/22A is operated in Mode 1. An access cycle begins when the 68000 places a valid address on the address bus and asserts  $\overline{AS}$ .  $\overline{AS}$  is then clocked with a 74AS74 flip-flop. The output of the flip-flop is used to produce ADS to the DP8420A/21A/22A.

Chip Select ( $\overline{\text{CS}}$ ) is generated by a 74AS138 decoder. If a refresh or Port B access had been in progress, the 8420A/21A/22A would hold off the access by inserting wait states in the access cycle. The DP8420A/21A/22A will place the row address on the DRAM's address bus and assert RAS. After guaranteeing the row address hold time, tRAH, the DP8420A/21A/22A will place the column address on the DRAM's address bus and assert CAS.

### DESIGN #3 TIMING AT 16.667 MHz

Clock Period = Tcp16 = 60 ns @ 16.667 MHz \$400b: ADS Asserted Setup to CLK High = Clock Period - 74AS74 Delay Max

= Tcp16 - TphI = 60 ns - 9 ns

= 51 ns @ 16.667 MHz

\$401 CS Asserted Setup to ADS Asserted

= 11/2 Clock Periods + Min 74AS74 Delay

Max Clock to Address

74AS138 Delay

$= 1\frac{1}{2} \text{Tcp16} + \text{TphI} - \#6 - \text{TphI}$

= 90 ns + 4.5 ns + 50 ns - 9 ns

= 35.5 ns @ 16.667 MHz

\$407 & \$404: Address Valid Setup to ADS Asserted

= 11/2 Clock Periods + Min 74AS74 Delay - Max Clock to Address

$= 1\frac{1}{2} \text{Tcp16} + \text{TphI} - #6$

= 90 ns + 4.5 ns - 50 ns

= 44.5 ns @ 16.667 MHz

\$405: ADS Negated Held from CLK High

Min 74AS74 Delay

= 4.5 ns @ 16.667 MHz

# 47: DTACK Setup Time

= Clock Period - 74AS74 Delay Max

= Tcp16 - TphI

= 60 ns - 9 ns

= 51 ns @ 16.667 MHz

### **RAS LOW DURING REFRESH**

tRAS = Programmed Clocks

- [(CLK High to Refresh RAS Asserted)

- (CLK High to Refresh RAS Negated)]

= Tcp16 + Tcp16 + Tcp16

+ Tcp16 - \$55

= 240 ns - 6 ns

= 234 ns @ 16.667 MHz

tRP

= (Programmed Clocks - 1) -[(AREQ to RAS Negated) -(CLK to RAS Asserted)]

= Tcp16 + Tcp16 - \$50

= 120 ns - 16 ns

= 104 ns @ 16.667 MHz

### **RAS PRECHARGE PARAMETERS**

= Programmed Clocks - Clock to  $\overline{AS}$ Negated - [( $\overline{AREQ}$  to  $\overline{RAS}$  Negated) (CLK to RAS Asserted)]

### **tRAC AND tCAC FOR DRAMs**

Timing is supplied for the system shown in Figure 7. Since system and DRAM times vary, the user is encouraged to change the following equations to match his system requirements. Timing has been supplied for systems with 2 wait states. If DELCLK is not a multiple of 2 MHz, the timing for tRAH and tASC will increase or decrease according to the times given in the data sheet. The  $\overline{ADS}$  to  $\overline{RAS}$  and  $\overline{ADS}$  to CAS will also have to be changed depending on the capacitance of the DRAM array.

1 wait state \* using 1 BANK with no transceivers

trac =

$$s4 + sw + sw + s5 + s6 - 74AS74$$

Delay -  $\overline{ADS}$  to  $\overline{RAS}$  - Data Setup

=  $21/_2$  Tcp16 - Tphl -  $$402 - $27$

= 150 ns - 9 ns - 25 ns - 10 ns

= 106 ns @ 16.667 MHz Using 8420-25 w/Light Load

2 wait states \* uses 4 banks with tranceivers \*

= 155 ns @ 16.667 MHz

### Design #3 Programming Bits

| Bits       | Description                                                         | Value                      |  |

|------------|---------------------------------------------------------------------|----------------------------|--|

| R0, R1     | $\overline{RAS}$ Low Time = 2T $\overline{RAS}$ Precharge Time = 2T | R0 = 0<br>R1 = 1           |  |

| R2, R3     | DTACK Generation Modes<br>for Non-Burst Accesses                    | R2 = 1<br>R3 = 0           |  |

| R4, R5     | DTACK Generation Modes<br>for Burst Accesses                        | R4 = u<br>R5 = u           |  |

| R6         | Add Wait States with WAITIN                                         | R6 = u                     |  |

| R7         | DTACK Mode Select                                                   | R7 = 1                     |  |

| R8         | Non Interleaved Mode                                                | R8 = 1                     |  |

| R9         | Staggered or All RAS REFRESH                                        | R9 = u                     |  |

| C0, C1, C2 | Divisor for DELCLK<br>(+8 for 16 MHz)                               | C0 = 0<br>C1 = 1<br>C2 = 0 |  |

| C3         | +30 REFRESH                                                         | C3 = 0                     |  |

| C4, C5, C6 | RAS, CAS Configuration Mode *Choose All CAS Mode                    | C4 = u<br>C5 = u<br>C6 = u |  |

| C7         | Select 15 ns Column Address Setup                                   | C7 = 1                     |  |

| C8         | Select 15 ns Row Address Setup                                      | C8 = 1                     |  |

| C9         | CAS is Delayed to the Next Rising<br>CLK Edge During Writes         | C9 = 1                     |  |

| В0         | The Row/Column Bank Latches<br>Are Fall Through Mode                | B0 = 1                     |  |

| B1         | Access Mode 1                                                       | B1 = 1                     |  |

| ECAS0      | CAS Not Extended Beyond RAS                                         | ECASO = 0                  |  |

# $u = user \, defined \,$

<sup>\*</sup>see previous page for 0 WAIT STATES during writes

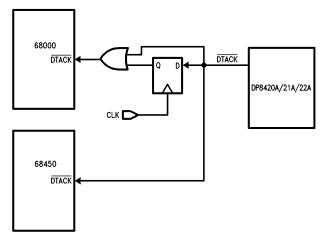

# Additional Circuitry for Design #1 Using the 68450 DMA Controller

TL/F/9732-8

Because the 68450 samples DTACK on a positive edge of CLK and the 68000 samples DTACK on the negative edge, additional circuitry must be added to produce the two DTACK signals. The DTACKs must be produced different to ensure RAS low time after an access delayed by a refresh. The programming bits must also be changed as follows:

For O WAITSTATES

R2 = 0 R3 = 1 FOR /DTACK OF 1/2

For 1 WAITSTATE

R2 = 0 R3 = 1 R6 = 0 FOR /DTACK OF 1 1/2

Tie the DP8420 signal WAITIN low for 1 waitstate and high for 0 waitstates. All timing except for the following should still apply. Times with a "#" refer to the 68000 data sheet. Times with a "!" refer to the 68450 data sheet and times with a "\$" refer to the DP8420A/21A/22A data sheet.

DTACK Setup Time \$47:

- = 1/2 CLOCK Period 74AS74 CLOCK to Q - 74AS32

- $= \frac{1}{2} \text{Tcp10} \text{TphI} \text{TphI}$

- = 50 ns 9 ns 6 ns

- = 35 ns @ 10 MHz

- = 1/2 Tcp8 TphI TphI = 62.5 ns - 9 ns - 6 ns

= 47 ns @ 8 MHz

DTACK Setup Time (68450)

- = 1/2 CLOCK Period CLOCK to DTACK

- $= \frac{1}{2} \text{Tcp10} \$18$

- = 50 ns 28 ns

= 22 ns @ 10 MHz

- $= \frac{1}{2} \text{Tcp8} \$18$

- = 62.5 ns 33 ns

- = 29 ns @ 8 MHz

All other 68450 times are the same as the 68000.

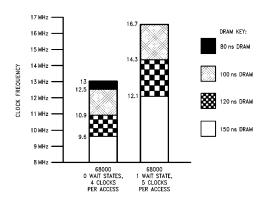

**DRAM Speed Versus Processor Speed,** (DRAM Speed References the RAS Access Time, tRAC, of the DRAM. **Using DP8422A-25 Timing Specifications)**

TL/F/9732-9

Lit. # 100538

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation

1111 West Bardin Road

Arlington, TX 76017

Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 **National Semiconductor**

Europe Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80

National Semiconductor Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408